IPC300

IEEE1588v2 (PTP) EVB - Boundary, Slave and Master Clock

Overview

The IPC300 EVB – IEEE1588v2 Boundary and Master/Slave Clock enables equipment vendors and ASIC vendors to evaluate the IPC9000, IPC1710, IPC1603 chip on FPGA.

The IPC9000/IPC1710/IPC1603 is optimized for providing high quality frequency synchronization, phase alignment and accurate Time of Day (ToD) distribution over packet switched networks with the flexibility to operate either as PTP BC and/or Master and/or Slave.

With the IPC9000/IPC1710/IPC1603, the use of PTP is allowing leveraging the IP network for distributing the clock to the clients hence lowering the total network deployment and maintenance expenditures by reducing the number of GPS receivers to the minimum required.

The IPC300 incorporates IPClock’s state-of-the-art IPC9000/IPC1710/IPC1603 designed to meet packet switched networks inherent impairments with proved excellent clock synchronization performance.

Typical applications for IPC9000/IPC1710/IPC1603 include:

- Telecom

- Cellular IP backhauling

- Aerospace and defense

- Smart Grid

- Homeland security

- Passive Optical Networks (PON)

Description

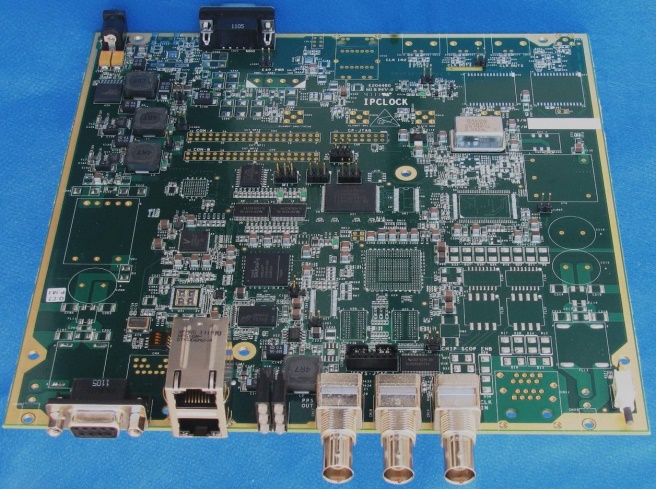

The IPC300 is an evaluation kit for the IPC9xxx, IPC17xx and IPC1603. The IPC9xxx, IPC17xx and IPC1603 utilize IPClock’s state-of-the-art technology for IEEE 1588 boundary, master and slave clocks optimized for providing high quality frequency synchronization and Time of Day (ToD) over packet networks. The IPC9xxx, IPC17xx and IPC1603 are implemented as chip on FPGA leveraging Xilinx® Spartan™ 6 FPGA, using 8MB of FLASH memory and 64MB of DDR II memory. The IPC300 has CLK IN, CLK OUT and PPS OUT clock interfaces via BNC connectors, 100/1000 Mbps Ethernet connection via RJ45, RS232 TOD interface via DB9 connector. The IPC300 can be managed by the user via the RS232 management port. The IPC300 has several LED indications: system power, device status (pass, alarm, fail), clock state (Free Run, Holdover, Trace, Lock). The IPC300 enable the user to explore the entire APIs set of IPClock’s devices by using simple CLI.

Features

CLK IN

1PPS from GPS

CLK OUT

1.544MHz, 2.048MHz, 10MHz

PPS OUT

1PPS

TOD

ToD Message Protocol: NMEA

Network Interface

100/1000 Base-T Ethernet

Management and Control

CLI based configuration and management via RS-232

IEEE1588v2

IEEE1588v2 PTP

G.8265.1

G.8275.1

Boundary Clock

Master / Slave

Unicast / Multicast

ITU-T G.8261 compliant

LEDs

PWR: Power

STAT: Status

LK/TR: Lock/Trace

HO: Holdover

FR: Free Run