# IPC9840

## IEEE 1588 Boundary, Slave and Master Clock - System on Chip (SoC)

### **About IPC9840**

The IPC9840 utilizes IPClock's state-of-the-art IEEE 1588 v2 technology optimized for providing high quality frequency synchronization and Time of Day (ToD) over packet transport networks. Clock synchronization is required by many wireline and wireless applications including 3G, 4G-LTE, 5G, smart grid, industrial automation and aerospace & defense. The IPC9840 is application-agnostic, cost effective, standard compliant IEEE 1588 v2 BC/Slave/Master, supporting G.8261, G.8265.1, G.8275.1 and G.8275.2. The IPC9840 is designed for easy field upgrades to support future enhancements as well as future synchronization standards.

The IPC9840 is a System on Chip (SoC) leveraging Xilinx® Zynq FPGA supporting 16MB of FLASH memory and 128MB of DDR3 memory.

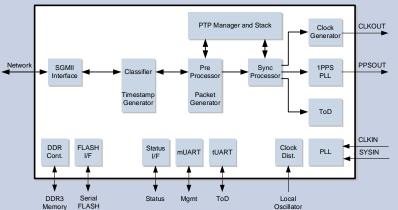

### **IPC9840 Functional Block Diagram**

The IPC9840 can be set to operate as either IEEE 1588 Boundary clock or Master clock or Slave clock. The IEEE 1588 protocol is a bidirectional protocol requiring all ports to transmit and receive IEEE 1588 packets. Each packet received its time-stamp by the Timestamp Generator and classified by the Classifier. In the case the packet is IEEE 1588 packet it is sent to the Pre-Processor along with its timestamp. The Pre-Processor is transferring the received general packets to the PTP Manager and Stack for further processing. In the case of IEEE 1588 event packet the Pre-Processor compensate for part of the packet network impairments and prepare the data for the Sync Processor. The Sync Processor is comprised of a suite of algorithms that processes the data and controls the 1PPS PLL, the programmable clock output of the Clock Generator, and the ToD. The ToD is communicating with the ToD UART utilizing the NMEA protocol for either providing or getting the ToD from a GPS. The IEEE 1588 packets are transmitted by the Packet Generator which is controlled by the PTP Manager and Stack. Each packet transmitted is time-stamped by the Timestamp Generator and this timestamp is either embedded into the packet or sent to the Pre-Processor depending on the packet type and selected mode of operation.

#### **Main Features and Benefits**

- Standalone IEEE 1588 v2 standard compliant Boundary Clock (BC) and Master/Slave System on Chip (SoC)

- Excellent synchronization performance over most extreme packet transport network conditions

- Slave meets 3G, 4G-LTE and 5G synchronization requirements

- Adaptive to network impairments

- Typical lock time better than 10 sec

- Slave ToD phase error is better than ±1µsec, and frequency accuracy is better than 16ppb, on a managed 10switch GbE network under ITU-T G.8261 conditions (\*)

- SGMII interface

- Hybrid IEEE 1588/SyncE support.

Requires external SyncE PLL.

- Supports APTS (Assisted Partial Timing Support)

- Supported IEEE 1588 profiles: G.8265.1, G.8275.1 and G.8275.2

- Supports up to 128 slaves/channels

- Supports Unicast/Multicast

- Supports one step / two steps

- Low total cost of ownership

- Zero touch approach can make external CPU redundant

- Upgradeable by software

- Easy adding of enhancements and supporting emerging clock synchronization standards

- Operates with 20MHz TCXO or OCXO

- Interfacing generic PHY

- Modes of operation: Free run, Trace, Lock and Holdover

- Utilize Xilinx's Zynq FPGA -XC7Z7010-2CLG225I

<sup>(\*)</sup> The performance tested under the ITU-T G.8261 tests suite provide an indication for IPClock's technology capabilities and is not guaranteed across all types of network elements and networks conditions. Please contact IPClock's support for more information.

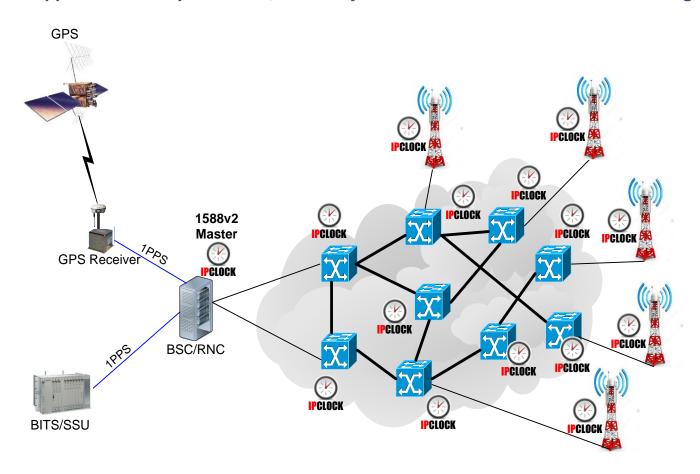

## Typical Application Example: Master, Boundary & Slave Clocks for Cellular Backhauling